Встречающаяся с высокой частотой проблема с ошибкой msvcr100, а также с некоторыми другими библиотеками dll, затрагивает пользователей Windows 10. Эта ошибка проявляется в различных вариантах, что указывается в появляющемся предупредительном сообщении, заменяющем запуск необходимого приложения.

Давайте проанализируем, что подразумевает данная ошибка, каковы её потенциальные источники, и, что наиболее важно, как её можно исправить, чтобы необходимые программы запускались в дальнейшем без лишних сложностей и затруднений.

Что обозначает ошибка с файлом msvcr100.dll и почему она возникает?

Возникновение ошибки, связанной с файлом msvcr100.dll, может указывать на его повреждение, нехватку на компьютере или его удаление. Также такая проблема может возникнуть при процессе установки операционной системы или соответствующего программного обеспечения.

Динамические библиотеки DLL, такие как PhysX, DirectX и Visual C++, часто входят в состав операционных систем после их установки. Для выявления причины ошибки, связанной с файлом msvcr100.dll, необходимо установить, какой программный пакет использует эту динамическую библиотеку в качестве компонента.

В данном контексте обсуждается программный дистрибутив Windows, а именно Visual C++ 2010. Этот пакет играет ключевую роль в системе, так как включает файлы языка C++, который является основным инструментом для создания широкого спектра современного программного обеспечения, от игр до системных утилит.

Как исправить ошибку файла msvcr100.dll?

Перед тем как начать работу над задачей, стоит предупредить энтузиастов о риске загрузки файлов с непроверенных сайтов, которые часто оказываются на первых местах в результатах поиска. В таких случаях мошенники могут маскировать вредоносные программы под названиями стандартных системных файлов, что может привести к нежелательным последствиям.

Важнее то, что необходимая библиотека Visual C++ 2010, включая отсутствующий файл msvcr100.dll, доступна для загрузки на официальном сайте Microsoft. Рекомендуется получать её прямо от производителя, что обеспечит надёжность. Варианты для систем x86/x64 предназначены для 32-битных и 64-битных операционных систем соответственно. В случае использования 64-битной системы, настоятельно рекомендуется установить оба пакета.

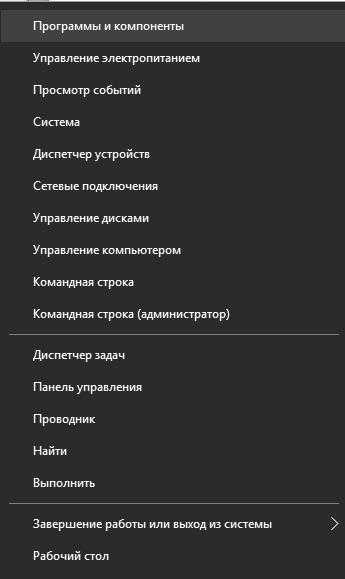

Давайте разберем пошаговый процесс установки загруженного программного обеспечения. Во-первых, необходимо проверить, установлен ли на вашем компьютере Visual C++ 2010. Для этого щелкните правой кнопкой мыши по кнопке «Пуск» и выберите первый пункт в контекстном меню «Программы и компоненты».

Откройте раздел «Программы и компоненты» в диалоговом окне меню «Пуск».

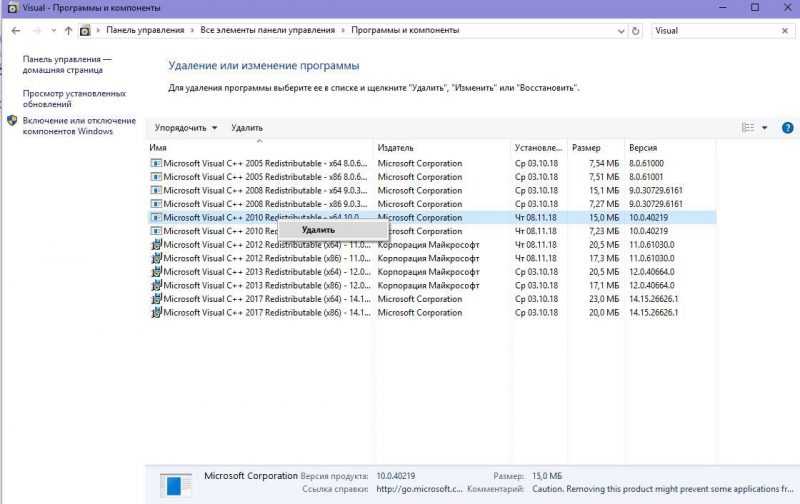

Вы увидите окно, в котором представлены все программы, установленные на вашем компьютере. Чтобы облегчить процесс поиска, введите «Visual» в системную строку поиска, и система выдаст список всех установленных версий пакета Visual C++ Redistributable.

Ищем наличие Microsoft Visual C++ 2010 в списке, и в случае его обнаружения, производим удаление.

Если после установки версии 2010 возникает ошибка, связанная с msvcr100.dll при запуске конкретной программы, рекомендуется удалить текущую установку и повторно установить её с помощью ранее загруженного установщика.

Установка выполняется чрезвычайно легко: запустите скачанный файл установки и проинсталлируйте дистрибутив, как и любую другую программу. Завершив процесс, рекомендуется перезагрузить компьютер и протестировать функциональность недавно установленного программного обеспечения.

Есть альтернативный подход для решения данной проблемы, если первоначальный метод оказался неэффективным. Решение состоит в загрузке и установке файла msvcr100.dll, а затем в копировании его в соответствующую системную папку. Однако будьте осторожны: избегайте загрузки такого рода файлов из ненадежных источников!

Для начала следует извлечь содержимое загруженного архива и затем переместить файл из него в две ключевые системные папки.

C:windowssystem32

C:windowsSysWOW64

После выполнения указанных действий, производим перезагрузку компьютера и вновь пытаемся запустить программное обеспечение, которое ранее не запускалось.